# Device Requirements for Optical Interconnects to Silicon Chips

Optics may allow interconnects to continue to scale to match the processing ability of future electronic chips, though very-low-energy optoelectronic devices and novel compact optics will be needed.

By DAVID A. B. MILLER, Fellow IEEE

**ABSTRACT** | We examine the current performance and future demands of interconnects to and on silicon chips. We compare electrical and optical interconnects and project the requirements for optoelectronic and optical devices if optics is to solve the major problems of interconnects for future highperformance silicon chips. Optics has potential benefits in interconnect density, energy, and timing. The necessity of low interconnect energy imposes low limits especially on the energy of the optical output devices, with a  $\sim$ 10 fJ/bit device energy target emerging. Some optical modulators and radical laser approaches may meet this requirement. Low (e.g., a few femtofarads or less) photodetector capacitance is important. Very compact wavelength splitters are essential for connecting the information to fibers. Dense waveguides are necessary onchip or on boards for guided wave optical approaches, especially if very high clock rates or dense wavelength-division multiplexing (WDM) is to be avoided. Free-space optics potentially can handle the necessary bandwidths even without fast clocks or WDM. With such technology, however, optics may enable the continued scaling of interconnect capacity required by future chips.

KEYWORDS | International Technology Roadmap for Semiconductors (ITRS) roadmap; optical interconnections; optical modulators

#### I. INTRODUCTION

Optical fiber has already taken over the task of longdistance communications from electrical cables and is increasingly advancing in connections between different parts of large electronic systems [1]. Substantial recent

Manuscript received December 2, 2008. First published June 10, 2009; current version published June 12, 2009. This work was supported by the Interconnect Focus Center. The author is with the Ginzton Laboratory, Stanford University, Stanford, CA 94305-4088 USA (e-mail: dabm@ee.stanford.edu).

Digital Object Identifier: 10.1109/JPROC.2009.2014298

efforts have focused on using optics on circuit boards [2], but wires still dominate all short-distance communications inside information-processing machines, especially on integrated circuit chips and on circuit boards.

As clock speeds and wiring density inside machines have increased, however, interconnection through wires has increasing difficulties [3]-[8]. Now the limited capacity of electrical interconnects is a problem for systems not only on the backplanes and busses between boards but also at the shorter distances between chips and even on chips. Physical arguments for why optics could help interconnections have been presented [9], [10]. Recent systems proposals have advocated optics on-chip through improved architectures enabled by optics [11], [12]. The purpose of this paper is to establish targets for research in optoelectronic and optical devices if optics is to solve the central interconnect problems to and on silicon processing chips.

This paper is unavoidably speculative. We have to try to project where electronic chips and electrical interconnect technology will be in the future and what the demands on interconnects will be. We also have to anticipate the performance of electronic, optoelectronic, and optical technologies that in many cases do not exist yet. Some of the speculation is unavoidably simplistic or even naïve. There is, however, little doubt that interconnects are now and will be increasingly a major limitation on informationprocessing systems. There is also little doubt that the physics of optics offers potential solutions. At least, we hope to show scaling trends, key technological requirements, and promising opportunities.

In Section II, we start by comparing the underlying physics of electrical and optical interconnects. The energies and densities required in future interconnects are discussed in Section III. In Section IV, we discuss the requirements for optical systems for interconnects, and in Section V we draw some conclusions from these energy and density arguments for optoelectronic devices and systems. We summarize our conclusions in Section VI.

### II. PHYSICS OF ELECTRICAL AND OPTICAL INTERCONNECTS

We have discussed the comparison between the physics of optical and electrical interconnects previously [6], [9], [10], [13], [14]. Underlying the contrast is the very high carrier frequency of optical signals—on the order of 200-1000 THz for corresponding free-space wavelengths of  $\sim$ 1.5  $\mu$ m to 300 nm. The short wavelength of light means that dielectric waveguides (which can have very low loss) can be used to guide the waves. Optics therefore avoids the metal waveguides that are essential for confining the radiofrequency waves of electrical interconnects, and hence also avoids the resistive loss physics that dominates the propagation loss and distortion of electrical lines. The very high carrier frequency of optics means that the high-speed modulation of optical beams makes practically no difference to their propagation, at least over the size scale of information-processing machines. Hence, (modulation-) frequency-dependent crosstalk and reflection is avoided; an optical system designed for one signal modulation frequency will work for higher modulation frequencies. Going along with the high frequency and short wavelength is that fact that the photon energy is large (~0.8 to 4 eV for the 200-1000 THz frequency range), which means that optical signals are created and detected quantum mechanically, in contrast to the classical currents and voltages of electronics. This quantum mechanical nature leads immediately to voltage isolation in all optical interconnects, and to a process called quantum impedance conversion [9], [13] in optical links that could save interconnect power.

These differences in physics lead to three specific major possible practical advantages for optical interconnects.

1) Interconnect Density: Optics avoids a key limit to the density of information that can be sent over relatively long distances. Because of the resistive loss in electrical lines, in lines without repeater amplifiers and for signaling limited by eye closure (rather than, say, the Shannon limit given by noise), the bit rate on electrical lines is limited to

$$B \le B_o \frac{A}{L^2} \tag{1}$$

where A is the cross-sectional area of the wiring, L is the length of the wires, and  $B_o$  is a constant.  $B_o \sim 10^{16}$  b/s for the resistive-capacitive lines that are typical on chip, a slightly smaller number for inductive-capacitive lines with resistive loss (RLC lines), and  $B_0 \sim 10^{17} - 10^{18}$  b/s for offchip equalized RLC lines presuming that the receiver can operate with up to 20 dB power loss in the line [6]. (The  $B_o \sim 10^{17}$  number corresponds to realistic equalized cables or printed circuit board traces and the 10<sup>18</sup> number is for ideal equalized lines.)

The fact that the ratio  $A/L^2$  is dimensionless means that once we have filled all available space with wiring, the bitrate capacity of the system cannot be increased by making the whole system either bigger or smaller. To exceed these capacities, some change of interconnect technology is required; electrically we would have to move towards modem techniques to try to approach the Shannon limit to capacity, with a corresponding increase in the electronic complexity and the possibility of increased power dissipation overall.

Since optics does not have this resistive loss physics limiting it, it can be particularly attractive for relatively long lines with high data rates and limited cross-sections. Additionally, because the carrier frequency is so high, there is a very large amount of available spectrum allowing wavelength-division multiplexing (WDM) that could increase the aggregate bit rate of a given optical beam well beyond the modulation rate possible on any one channel.

2) Interconnect Energy: Optics may be able to save energy in interconnection because it is not necessary to charge the line to the operating voltage of the link [9], [13]. When we communicate electrically, we charge up the whole line (or at least a section of it whose length corresponds to the pulse length) to at least the signaling voltage. Though that voltage need not be the logic voltage—low swing signaling is now common for signals on backplanes, for example [15]-[17], and has recently been advocated also for on-chip use [18]-[20]—this can be a significant energy, a total energy of

$$E_{\rm s} \ge C_{\rm l} V_{\rm r}^2 \tag{2}$$

where  $C_l$  is the capacitance of the line (or at least the portion charged by the signal pulse) and  $V_r$  is the signaling voltage. Since the capacitance of all well-designed electrical lines is similar ( $\sim$ 2 pF/cm or 200 aF/ $\mu$ m) (see, e.g., [6]), this energy cannot easily be reduced other than by reducing voltage swing.

By contrast, optical interconnects use quantum sourcing and detection of the signal, which makes the classical voltage in the medium not directly relevant (quantum impedance conversion [13]). In optics, the relevant energy for comparison instead is the optical energy required to discharge the total capacitance  $C_d$  of the photodetector and the electrical input to which it is connected by the required signal voltage, i.e.,

$$E_p \ge C_d V_r \frac{\hbar \omega}{e} \tag{3}$$

where the voltage  $\hbar\omega/e$  is numerically equal to the photon energy in electron-volts. (Here for simplicity we assume a photodetector of unit quantum efficiency, i.e., one electron per photon.) The inequality in (3) accounts for

the loss in the optical link and the additional energy cost of the optical output device.

Optics has the potential to win here to the extent that  $C_d\hbar\omega/e < C_lV_r$ . Since the electrical signaling voltage  $V_r$  might be small (e.g., 100 mV or less) compared to  $\hbar\omega/e$  (e.g.,  $\sim 1$  V), optics wins only if  $C_d \ll C_l$  (e.g., by a factor of ten or more). Hence optics can only win in this energy regard if the line is relatively long and the total detector/input capacitance  $C_d$  is small. For example, for a hypothetical total input capacitance  $C_d \sim 1$  fF in some very tightly integrated photodetector/transistor combination, the line capacitance  $C_l$  we are avoiding would need to be at least 10 fF for our example numbers, which corresponds to at least 50  $\mu$ m length at 200 aF/ $\mu$ m.

This particular 50  $\mu$ m break-even length for optics is arguably based on very favorable assumptions for optics; not only does it presume a very low detector capacitance but it also neglects the loss in the optical line and the inefficiency of conversion from electrical to optical signals. More detailed studies give longer crossover lengths for the energy benefit of optics [8], [10], [21]–[25] or are more pessimistic [26]–[28]. This argument does, however, show that there is potentially an energy benefit for optics, one that becomes progressively better as we consider longer lines and lower detector capacitance.

3) Clock and Signal Timing: Optics may be able to deliver and retain very precise timing in clocks and signals [29]-[31]. Optical signals, including short (e.g., picosecond) pulses, do not spread substantially in propagating over the size scale of an information-processing machine. Additionally, short pulses can directly deliver very precise timing edges and could have other benefits [32], including reducing latency [33] and improving signal timing [34]. Optics could be useful for reducing the number of levels in the clock distribution tree [24], [30], thereby reducing clock power dissipation and improving jitter, though there is likely not enough available optical power to clock the entire chip [30]. Multichannel (e.g., WDM or parallel freespace array) signals could, however, retain their relative timing, thus avoiding having to compensate separately for timing variations between channels [35]; only one clock channel or one clock recovery would be required for an entire multichannel line—a significant possible benefit for optics. In what follows, we concentrate mostly on energy and density in interconnects, though timing benefits could also be important.

The basic limiting issues of electrical interconnects on chips have been known for some time (e.g., [7]) and led, for example, to the shift to copper wiring on chips to reduce resistance and improve interconnect speed. One technique that is used routinely to avoid some of the limitations on chip is to break the line into smaller segments through the use of repeater amplifiers. Since the length L of any given segment can then be short, the limitation from  $B_0A/L^2$  can be avoided, though one price is a low effective signal velo-

city on such a repeated line (see, e.g., [10]), adding significant signal delay. Electrical designers have equalization circuit approaches to help with limitations of wiring such as signal distortion and loss (see, e.g., [15], [16], [18]–[20], and [36]), but such approaches add complexity and power and cannot ultimately avoid the underlying physics that limits wires. There are also arguments now that optics might particularly enable networks at short distances, for example, for chip-scale multiprocessors, with additional potential energy reduction and performance improvement [11], [12].

Despite these problems of wiring and the arguments in favor of optics for interconnects to or even on the silicon chip, there is essentially no such use today. There are many possible reasons for this absence of short-distance optical interconnects, but certainly cost targets for introduction of optics at short distances are extreme because wires on chips and boards are very inexpensive. Being able to make the necessary optical and optoelectronic components in a lowcost process compatible with silicon electronics may well be essential for any commercial introduction of optical interconnects. Silicon photonics has advanced substantially in recent years, and has demonstrated many of the key components in such integrated processes (see [37]-[39] for recent reviews and collections of work). Still, however, as we discuss below, the requirements on the optical and optoelectronic devices and their integration are very challenging if optics is to be exploited on any large scale at such short distances, and there are some missing pieces in the technology and devices. Below, we attempt to clarify those demands on devices to give clear focus to research efforts to bring about mainstream use of optical interconnects.

## III. ENERGY AND DENSITY REQUIREMENTS FOR INTERCONNECTS

# A. Power Dissipation in Chips and Information-Processing Systems

Power dissipation in information-processing systems is a major limitation at many levels, including on complementary metal—oxide semiconductor (CMOS) chips themselves. The International Technology Roadmap for Semiconductors (ITRS)<sup>1</sup> states<sup>2</sup> that the amount of heat that can be removed from a chip in a cost-effective manner is about to reach a plateau, saturating at about 200 W, and that power management is now the primary issue across most application segments. The inability to handle higher powers limits the performance of chips.

There are many sources of power consumption in electronic systems. Interconnects are, however, a major and growing contributor. Approximately 50% of microprocessor power was consumed by the interconnect at the  $\sim$ 130 nm

<sup>&</sup>lt;sup>1</sup>See http://www.itrs.net/Links/2007ITRS/Home2007.htm.

<sup>&</sup>lt;sup>2</sup>See http://www.itrs.net/Links/2007ITRS/ExecSum2007.pdf.

technology node [40] (approximately the technology in the year 2002), and this is expected to rise to  $\sim$ 80%.

Overall power consumption is an issue too in the economics of large systems. The cost of powering a server over its lifetime is now estimated to be comparable to the purchase cost of the server hardware [41]. The power consumption of information technology is now so large that it is starting to be environmentally significant. Data centers alone were estimated to consume on the order of 1% of all electricity in 2005 (1.2% in the United States, 0.8% worldwide) by one estimate [42] and 1.5% of U.S. electricity in 2006 by another [43], with that latter estimated power consumption rising by about a factor of two by 2011 if historical trends continue. The central processing unit (CPU) in one provider's servers consumed between  $\sim$ 27% and  $\sim$ 57% of the total server power in the 2005–2007 timeframe [44]. Presuming 50% of CPU power is in the interconnects, and taking the lower estimate of 27% of the server power in the CPU would still mean that, in the United States, server interconnect power exceeds the total power generated from solar energy in 2007 [45]. The Global eSustainability Initiative (GeSI) estimates [46] that the information and communications technology (ICT) industries in 2002 are responsible for ~0.5 GtCO<sub>2</sub> (gigatons of carbon dioxide) emission in a year, out of a total global emission of 40 GtCO2, corresponding to ~1.3% of all emissions. This study estimates the ICT contribution will rise to  $\sim$ 1.4 GtCO<sub>2</sub> by 2020, out of a total of 53 GtCO<sub>2</sub>, that is, 2.6% of carbon emissions. This report advocates that ICT will lead to substantial overall savings in carbon emissions because of the efficiencies ICT will enable in other areas, but still the overall emissions associated with ICT are significant in their own right.

Power dissipation, including a substantial contribution from interconnects, is therefore a problem that directly limits the performance of chips and increasingly is a significant factor in system economics and the environmental impact of information technology. Arguably, then, it would be very difficult to introduce a new solution for interconnects (such as optics) if it takes more power than the existing (electrical) approach, even if it promises other advantages.

## B. Energies and Interconnect Densities for Interconnects to and on Chips

To understand the targets for optical interconnects, we need to understand the energy dissipations and densities of electrical interconnects. (See also [8] and [21]–[23] for other analyses of the relative benefits of optics and electronics in energy and interconnect density.)

- Off-Chip Interconnects on Boards and Backplanes— Electrical Interconnects and Current Systems

- a) Current performance: First, let us look at current technology and demonstrated performance for off-chip electrical interconnects to backplanes or chip-to-chip con-

nections on boards. Several authors summarize recent results on transceiver energies for high-speed (i.e., ~4 Gb/s or faster) off-chip electrical interconnects [17], [47], [48]. Typical results have energies per bit of 2-30 pJ/bit in recent demonstrations. (1 pJ/bit is the same as 1 mW/(Gb/s); the latter is a more common way of stating the unit in the electrical interconnect literature, though the former relates more obviously to the physics of the interconnect devices.) The best current results for transceivers are  $\sim$ 2. 8-6.5 pJ/bit for board or backplane interconnects [17] and ~2 pJ/bit [16] for moderate length chip-to-chip interconnects with a relatively ideal electrical channel. Other recent work shows receivers for such links with  $\sim$ 1 pJ/bit at ~10 Gb/s rates [49], [50]. Capacitively coupled proximity communication directly between chips allows particularly high densities of interconnections with similarly low energies [51], and there is a variety of other approaches also for dense short vertical "threedimensional" (3-D) connections between chips or active circuit layers [52]. Recent work [53] shows energies as low as 80 fJ/bit in such 3-D capacitive connections in 130 nm silicon technology, for example, for face-to-face chips.

We have argued above that it is unlikely that any new interconnect technology can be introduced that takes more energy than the existing electrical approaches. The above electrical energy-per-bit numbers alone strongly suggest that if optical technologies are to take over a substantial fraction of off-chip interconnects on boards or backplanes, then the total (on-chip) system energy to run the optical interconnect cannot exceed ~1 pJ/bit. (See also the recent discussion of "energy per useful bit"—a metric that also factors in interconnect delay-by Krishnamoorthy et al. [55], which also advocates a 1 pJ target for this related metric.) Just as in electrical interconnects, there are many energy contributions other than the output device or line driver, so the energy per bit for any optical output device (modulators or light emitters) should be ≪1 pJ. To be sufficiently competitive to justify the introduction of optical interconnects, arguably we should require a reduction in overall energy consumption with the optics. Given that it may still be some time before introduction of optical interconnects to the chip as a mainstream interconnect technology, and at least the circuits used for electrical interconnects will continue to improve with the continuing improvement in silicon CMOS technology, arguably we should target system energies in the range of  $\sim$ 100 fJ/bit for optics. Such a system energy per bit argues for optical output device energies in the scale of 10 fJ/bit to a few tens of femtojoules per bit.

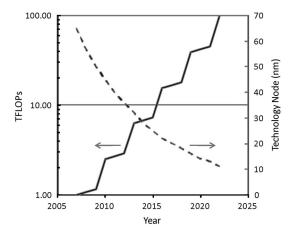

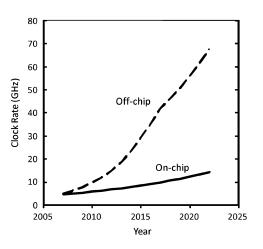

b) Future targets: To understand future energy targets for off-chip interconnects, we can look first at numbers from the ITRS roadmap. In Figs. 1–4, we graph some key numbers from this roadmap together with some other results we calculate below, and we summarize some key numbers in Table 1 for two specific target years, 2015 and 2022, as representative examples. For the later

Fig. 1. The technology node (a characteristic feature size) for silicon CMOS, and the projected number of FLOPs (units TFLOPs =  $10^{12}$  FLOPs), scaling by the product of the number of transistors times the on-chip clock rate, from a presumed 1 TFLOP in 2007 ([54]).

years, we also add projections assuming we retain constant numbers of bytes of off-chip interconnect per floating-point operation (bytes/FLOP or B/FLOP). All the numbers except the energies per bit, the floating-point operations per second (FLOPs), and the numbers at later years for constant bytes per FLOP come directly from the ITRS roadmap, and we use the numbers for high-performance application-specific integrated circuits (ASICs) from that roadmap. The ITRS numbers are based on some presumed scaling of technology or demand, though it is by no means clear that any evolutionary electrical approach would enable these numbers, a point made explicitly in the roadmap.

In these figures and in Table 1, for simplicity, we presume 1 bit/s for each hertz of off-chip clock frequency for each pad. [We could argue that 2 bit/s per hertz is achiev-

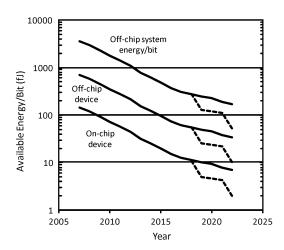

Fig. 3. The available energies per bit for interconnects, including the total available system energy per bit for off-chip interconnects (top lines), the energy per bit available for the optical output devices to drive the off-chip interconnect (middle lines), presumed to be 20% of the system energy per bit, and the energy per bit available for optical output devices to drive the on-chip global interconnects (bottom lines). The global on-chip interconnects are presumed to have five times the off-chip bandwidth. The solid lines presume the bandwidths from the product of the off-chip clock rate and the number of signal pins from the ITRS roadmap. The dashed lines presume that the number of bytes of off-chip interconnect per floating-point operation (i.e., the number of bytes/FLOP) is to be maintained in the later years. The middle lines also happen to represent the system energy/bit for on-chip global interconnects because we take that energy also to be five times the device energy for on-chip global interconnects.

able with non-return-to-zero signaling, but in compensation we could also argue that differential lines with two lines (and hence two pads per signal) would be required electrically.] Such a number should also be regarded as an

Fig. 2. Projected on-chip clock rate and the projected off-chip rate required to drive the chip input and output, according to the ITRS roadmap.

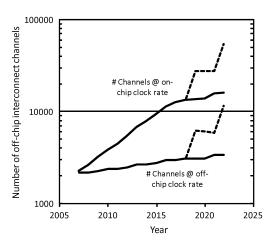

Fig. 4. Number of channels required to support the ITRS off-chip interconnect bandwidth [40], presuming either the ITRS off-chip or on-chip clock rate, respectively, for those channels (solid lines). The dashed lines show the corresponding numbers if the number of bytes/FLOP is maintained in the later years.

Table 1 Key Parameters for Technology Node, On- and Off-Chip Clock Frequencies, and Signal Pins From the ITRS 2007 Roadmap, and Calculated Total Input/Output (I/O) Data Rates and Available Energy per Bit for Off-Chip Interconnects, Assuming 20% of Chip Power Is Used for These

| Year                       | Tech. | On-   | Off-  | Signal   | Total  | fJ/bit |

|----------------------------|-------|-------|-------|----------|--------|--------|

|                            | Node  | Chip  | Chip  | Pins     | I/O    | for    |

|                            | (nm)  | Clock | Clock | 13303000 | (Tb/s) | Off-   |

|                            |       | (GHz) | (GHz) |          |        | Chip   |

| 2007                       | 65    | 4.7   | 4.88  | 2200     | 11     | 3500   |

| 2015                       | 25    | 8.5   | 29.1  | 2800     | 82     | 490    |

| 2022                       | 11    | 14.3  | 67.5  | 3420     | 230    | 170    |

| 2022<br>constant<br>B/FLOP | 11    | 14.3  | -     | -        | 780    | 50     |

upper bound, since it is based on the naïve assumption that all the signal pins could be handling high-speed I/O and all could be running at the maximum rate. We should note too that on the ITRS roadmap, achieving the off-chip clock rate for the later years is considered a problem for which manufacturable solutions are not known. Such an increased clock rate is projected in part because the number of pins on a chip is projected to grow only slowly (see [1] for a discussion of the projected relative growths). Nonetheless, this simple product of off-chip clock frequency and number of pads can be useful for scaling arguments.

To calculate the available system energy per bit for the interconnect in these figures and in Table 1, we make the arbitrary assumption that 20% of the total chip power is allocated to the off-chip interconnections, and another 20% to the on-chip interconnect. Given that we also need power for clocking and the logic operations themselves, these are arguably reasonable fractions. It is certainly difficult to argue that they should be substantially higher.

An alternative projection of off-chip interconnect requirements is to ask the capacity of that interconnect to keep up with the ability of the chip to perform computational operations. Such a projection would therefore be attempting to retain a given number of bytes/FLOP. The number of bytes (of communication to memory) per FLOP is a common metric in computer architectures [56], [57], with 1 byte/FLOP being a desirable number (though an increasingly difficult one to achieve) for connections to large amounts of memory. For example, Drost et al. [57] summarize bandwidths to different levels of the memory hierarchy in large machines. Those machines surveyed have  $\sim$ 1–10 bytes/FLOP for the connections to local cache memory, falling to  $\sim$ 0.02–0.5 bytes/FLOP for connections to the large, more distant memory. A related idea of the constancy of the ratio between processor power (in instructions per second) and I/O bandwidth (in bits per second) at 1 bit of I/O per instruction—known as Amdahl's balanced system law [59], [60]—is common in discussions of computer design [59], [60].

One recent experimental 275 mm<sup>2</sup> multiprocessor chip [54] performed 1 TFLOP operations per second, in

65 nm node technology, with a 4.27 GHz clock. Such a chip is broadly comparable to a hypothetical "ITRS 2007" 310 mm², 4.7 GHz clock-rate ASIC chip on the ITRS roadmap for the year 2007, which would have 2200 off-chip signal pads running at 4.88 GHz, corresponding to an upper bound of 11 Tb/s, or 1.3 Tbyte/s. Hence, dividing 1.3 Tbytes/s by 1 TFLOP, such a chip could hypothetically achieve  $\sim$ 1 byte/FLOP on our simplistic estimates of off-chip bandwidth from ITRS numbers. (Here, for simplicity, we consider one byte of communication as being either one byte going on chip or one byte coming on, i.e., our 1.3 Tbyte/s here is the sum of the rates on and off the chip.)

We can obtain a simple estimate of the capability of future chips to perform floating point operations using the ITRS predictions. The ITRS 2007 chip had an estimated 1106 million transistors per chip in 2007, scaling up by a factor of four to 2015. If we also scale the on-chip clock from 4.7 to 8.522 GHz, as suggested by ITRS—a factor of 1.8—then we predict a chip with  $\sim$ 4 × 1.8 × 1 TFLOPs = 7.2 TFLOPs in a simple scaling in 2015. The ITRS projections (as calculated above) give a presumed ~11 Tbyte/s bandwidth in 2015, so the ability to provide ∼1 byte/FLOP (actually 11/7.2 bytes/FLOP) would be retained for this hypothetical chip. Scaling to 2022, ITRS has the number of chip transistors increasing by a further factor of eight (to 35 391 million), and the on-chip clock rate increasing to 14.343 GHz, a further factor of 1.68. The chip performance on a simple scaling would increase to  $8 \times 1.68 \times$ 7.2 TFLOPs = 96.8 TFLOPs. We have plotted these simple scaling projections in Fig. 1. The ITRS projections, however, have an upper bound of only ~29 Tbyte/s offchip bandwidth, corresponding to only  $\sim$ 0.3 byte/FLOP, so the architecture would be significantly impacted by the lack of interconnect bandwidth. We see this discrepancy in the contrast between the solid and dashed lines in Fig. 4. To achieve 1 byte/FLOP would require  $\sim$ 780 Tb/s of off-chip bandwidth.

Whether or not current or future chips can in practice achieve a number as high as 1 byte/FLOP in connecting to off-chip memory is speculative. It is clear, though, that the off-chip interconnect in ITRS projections does not keep up with the ability of the chip to perform logic operations.

Another key point about such off-chip interconnect bandwidths is the energy available per bit. The ITRS roadmap has the power dissipation of chips saturating at  $\sim\!200$  W. Then for the off-chip bandwidth of 82 Tb/s of the ITRS 2015 chip, we have only  $\sim\!490$  fJ per bit of available energy; and, for the 230 Tb/s of the ITRS 2022 chip, we have only  $\sim\!170$  fJ. To have an interconnect that would keep a constant ratio of bytes/FLOP for the ITRS 2022 chip, we would have only  $\sim\!50$  fJ/bit available. These energies are the total system energies available per bit. For a hypothetical optical interconnect, we can only allocate a portion of that to the optical output device. In Fig. 3, we have plotted calculated off-chip optical output device energies assuming that the device consumes 20% of the

system energy per bit. On this basis alone, that energy is 97 fJ by 2015, falling to 34 fJ by 2022. To retain the ratio of bytes/FLOP, that energy falls to 10 fJ by 2022.

Given the current state of the art in electrical off-chip interconnects, which is in the range of 2 pJ or greater, arguably such electrical approaches with future technology might achieve the required  $\sim\!490$  fJ/bit in 2015. Whether electronic technology could handle further reductions in off-chip energy is a more open question. Such questions are the subject of ongoing research in electrical interconnects.

A second question for electrical interconnects is whether the off-chip wiring would have enough crosssectional area to handle the signals. One upper bound guideline for electrical interconnect densities is (1), which can project the minimum cross-sectional areas for connections of a given length when performance is limited solely by loss and distortion in high-quality lines and the lines are equalized with appropriate electronic circuits. Equation (1) does not, therefore, account for the additional problems of reflections and distortions from junctions, bends, and interlayer via connections in boards. It presumes point-topoint connections (i.e., no bus structures with multiple taps) and presumes the low-frequency skin effect with bulk copper conductivities. It also neglects dielectric loss. With a value of  $B_o \sim 10^{17}$  b/s, this bound would project that the cross-sectional area of wiring required might just be possible for 10 cm lines on boards for the 2015 and 2022 ITRS chips, at least if there are only a few chips to be connected in this way. Whether the backplane could provide enough cross-sectional area for 1-m-long wiring is more doubtful. If we were to ask for the 780 Tb/s of the hypothetical 1 byte/FLOP chip of 2022, for example, for 1-m-long connections the wiring would need a crosssection of at least  $\sim 80 \text{ cm}^2$ , which appears quite unrealistic. The issue of reducing the cross-sectional area of wiring is already one of the major reasons pushing the implementation of optical interconnects in larger systems [1], and we can expect this will continue to be a major practical reason at shorter distances also.

2) On-Chip Interconnects—Electrical Interconnects and Current Systems: Electrical wires have been, and will continue to be, extremely convenient and effective for on-chip interconnections. Their manufacturing cost is very low, and extremely complex multilayer interconnections can be fabricated.

The operating energies are low for all short interconnects; at  $\sim\!\!2$  pF/cm capacitance, even at 1 V signaling, the CV² energy cost is only  $\sim\!\!200$  aJ per bit for each micrometer of line length, which corresponds to  $\sim\!\!20$  fJ per bit for a 100- $\mu$ m-long line. For longer lines, however, the energies, at least for such simple "on/off" full-swing signaling, do start to become significant on the levels of energies we have been discussing. Simple 1 V signaling across a 2 cm chip would cost  $\sim\!\!2$  pJ per bit just for charging and discharging the line.

Density of interconnects is not a problem for short lines. For longer lines, breaking the line up into small segments with repeater amplifiers can avoid the bit-rate density limits such as those given by (1) (see, e.g., [3] and [10]), though this can lead to low effective signal propagation velocities and hence significant delays [3], [10]. Such repeater amplifiers also do not reduce the energy to send a bit. One key question in on-chip interconnects is whether energy per bit can be reduced for the longer "global" interconnects while still retaining sufficient density and limiting the delay in the interconnect lines.

The energies of on-chip electrical interconnects for the "global" lines with lengths in the range of 5 mm or more could be reduced from the  $\sim$  picojoule numbers calculated above through the use of low-voltage signaling. For example, recent work on on-chip interconnects has simulated a 1-cm-long complete interconnect, including clocking, at  $\sim$ 1 pJ per bit [18] in 90 nm silicon technology, using low-voltage differential signaling.

Another recent interesting suggestion to reduce on-chip electrical communication energy per bit is to use equalized lines on chip [19], [20]. Kim and Stojanovic [19], [20] have analyzed optimized on-chip lines, both with repeaters and with equalization circuits, for 5–15 mm lengths in 90 [19] and 32 nm [20] (year 2013) technology. The energy per bit for such a system depends greatly on the bandwidth density. Kim and Stojanovic consider densities of bits/second per micrometer of wiring layer width in a given wiring layer. Their numbers can be converted to bits/second per unit wiring layer cross-sectional area by dividing by the wiring layer total thickness. For example, in metal interconnect level 9 (M9), the total thickness of the wiring layer, including dielectrics, is  $\sim$ 1.4  $\mu$ m. They project, for example, that 15-mm-long on-chip repeated lines will consume  $\sim$ 300 fJ per bit in 32 nm technology for densities up to  $\sim 1.5 (\text{Gb/s})/\mu \text{m} (\equiv 1.1 (\text{Gb/s})/\mu \text{m}^2)$ , with larger energies for lower metal levels. At the same bit/second densities, they project that equalized lines would consume  $\sim$ 220 fJ/bit, though that energy would drop to  $\sim$ 54 fJ/bit for  $\sim 0.5$  (Gb/s)/ $\mu$ m( $\equiv 0.35$  (Gb/s)/ $\mu$ m<sup>2</sup>) bit-rate density. Increasing bit-rate densities beyond these numbers would apparently lead to substantial growth in energy for these equalized systems, so these bit-rate densities might be considered approximately the largest ones that lead to significantly lower energies compared to repeated lines.

We can compare these results to an equation of the form of (1). If we put a bit-rate density of 1.1 (Gb/s)/ $\mu$ m<sup>2</sup> for a 15-mm-long line into (1), then we obtain  $B_o \cong 2.5 \times 10^{17}$  b/s. Interestingly, this is a comparable number to the  $B_o$  values calculated for off-chip equalized RLC lines (for which  $B_o \sim 10^{17} - 10^{18}$  b/s), so this formula may be a useful empirical guideline also for these on-chip lines.

If we presumed we occupied the entire M9 layer of a 20  $\times$  20 mm chip with interconnects running at this density of 1.5 (Gb/s)/ $\mu$ m, then the total bit rate running through those interconnects would be  $\sim$ 30 Tb/s. For

shorter lines, Kim and Stojanovic estimate larger possible bit-rate densities and smaller energies—e.g.,  $3.5~({\rm Gb/s})/\mu{\rm m}$  with 130 fJ per bit for 10 mm lines in M9. Whether these are sufficient numbers for a high-performance chip at the 32 nm technology node of year 2013 is an open question. The off-chip aggregate data rate projected for the ITRS 32 nm node in high-performance ASICs is 2808 data pins running at 18.63 GHz = 52 Tb/s, which is broadly comparable to our calculated 30 Tb/s on-chip data rate for long wires for that node, and so such equalized electrical interconnect might provide the on-chip densities at least to drive the off-chip bandwidth for that node.

To answer the question of whether such electrical onchip interconnects could continue to handle the necessary on-chip capacity, we would need to answer the architectural question of how much on-chip data over what distance is needed for future high-performance chips. Wire length analysis has been performed for single microprocessors (see, e.g., the ITRS roadmap<sup>1</sup>). This analysis may, however, be of limited use for our purposes because it appears that on-chip architectures may be changing to ones with networks of large numbers of processors [chip multiprocessor (CMP) architectures]. As this happens, the individual processors become physically smaller with future generations, and so the physical wire length in them shrinks. If the clock rate in those processors remains substantially constant as they are shrunk—a concept that limits power dissipation—then the electrical interconnects within each processor can continue to work at the same bit rates as before while becoming shorter physically and hence consuming less energy per bit. If and when that architectural change takes place, the longer interconnects become those in the network that connect the individual processors, and so we should look at those networks to get another perspective on the issues for the longer wires on the chip.

As a representative example of future on-chip interconnect requirements for longer links, consider the hypothetical CMP of Owens et al. [60]. This chip, based on 2015 technology, at the 22 nm node, presumes a  $16 \times 16$  grid of 256 processor cores on a 400 mm<sup>2</sup> die. A mesh routing network with a total of 480 links each running at 1 Tb/s aggregate data rate connects each core to its neighbors. Each link consists of 144 physical wires, each 1.25 mm long, and each running at a chip clock rate of 7 GHz. The desired total power to run this network is 10 W. With a total bit rate of 480 Tb/s on all the links, there is, therefore, only 10 W/480 Tb/s = 21 fJ/bit available on this design. Their estimate of the electrical power to run such links, based on wires with repeater amplifiers, is 312.5 fJ/bit. Hence immediately we see that electrical power dissipation in the networks in CMP architectures is likely to be a substantial problem for aggressive future chip designs. Running the links just for this mesh network at the 312.5 fJ/bit would consume the entire 150 W chip power budget.

Note, incidentally, that this total on-chip bandwidth of 480 Tb/s for these moderately long (1.25 mm) links is about six times larger than the 82 Tb/s off-chip bandwidth capacity calculated above for the ITRS 2015 chip, though the bisection bandwidth (the bandwidth crossing a line across the chip) is targeted at 16 Tb/s for this example CMP chip [60].

Just what the relation should be between off-chip bandwidth and global on-chip bandwidth is not clear without making additional architectural and application assumptions, though it would be difficult to imagine that the on-chip global bandwidth could be significantly less than the off-chip bandwidth—the data going in and out of the chip has to go to and come from somewhere on the chip, and presumably those destinations and sources are not just around the edge of the chip. The numbers quoted above from Drost  $et\ al.\ [57]$ , with  $\sim 1-10$  bytes/FLOP for connections to local cache memory suggest on-chip bandwidths are likely much higher than off-chip bandwidths, perhaps as much as a factor of ten.

Hence, we should expect on-chip global bandwidth to be at least comparable to the off-chip bandwidth for a given chip, and possibly significantly larger. For illustration, we presume that the on-chip global bandwidth is five times larger than the off-chip bandwidth; though this factor is somewhat arbitrary, it is consistent with the 1-10 bytes/ FLOP from Drost et al. [57], and with the 480 Tb/s on-chip bandwidth of Owens et al. [60] for a chip we calculate to be capable of  $\sim$ 82 Tb/s off-chip interconnect. Hence, we take the targets for energies per bit for on-chip global interconnects to be  $\sim$ 5 times smaller than those for off-chip interconnects. Consequently, where we were looking for total system energies per bit ~1 pJ-100 fJ for off-chip interconnects, we could argue that we should be requiring system energies of  $\sim$ 200–20 fJ per bit for global on-chip interconnects. The specific projected numbers for the onchip system energy/bit from the ITRS scaling based on constant bytes/FLOP are the same as the off-chip device numbers shown in Fig. 3, so those lines also represent the on-chip system energy/bit. This is because we chose factors of 1/5 in both cases (off-chip device energy/bit  $\sim$ 20% of off-chip system energy/bit; off-chip bandwidth 20% of on-chip global bandwidth).

### IV. REQUIREMENTS FOR OPTICAL SYSTEMS

Before discussing optoelectronic device requirements in the next section, here we discuss some basic numerical targets required of the optics itself for optical interconnects that would meet the desired bandwidths. There are two broad categories of approaches—so-called "free-space" optics and guided wave optics. WDM is an additional option that may be particularly useful for the guided wave approaches and could be used in free-space systems also [35].

#### A. Off-Chip Interconnects on Boards and Backplanes

Optics can certainly avoid the kinds of density bounds encountered in electrical systems, e.g., as characterized by (1), for off-chip interconnects. One optical fiber, with a diameter of 125  $\mu$ m, on its own can carry more than 20 Tb/s of information [61], [62] in telecommunications systems, for example.

One key parameter for discussing optical systems is how many physical channels we need to carry the interconnect data rate. This number is the total data rate divided by the relevant clock rate. We plot numbers of channels in Fig. 4, where we show numbers of channels based on both off-chip and on-chip clock rates.

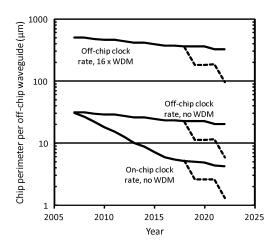

1) Waveguide Approaches: If we intend to take the data on and off the chip using waveguides that are connected around the perimeter of the chip, e.g., as waveguides on the board to which the chip is connected, then we are interested in the number of micrometers of perimeter needed for each of these channels. That number will determine what waveguide sizes are required on the board. For a chip area of 310 mm² as presumed on the ITRS roadmap, the total perimeter, assuming a square chip, is 70.4 mm. The resulting available chip perimeter per waveguide is shown in Fig. 5 for various assumptions.

a) Optical fibers: If we were to use conventional optical fibers, which have a diameter of 125  $\mu$ m, stacked side by side and butted against the chip edge, the calculations of Fig. 5 show that WDM would be essential at all

Fig. 5. Available width per waveguide channel for waveguides brought off the chip edge. Upper lines—channels running at the off-chip ITRS clock rate, and with 16 WDM channels on each waveguide. Middle lines—channels running at the off-chip ITRS clock rate, with one channel per waveguide. Lower lines—channels running at the on-chip ITRS clock rate, with one channel per waveguide. The solid lines presume the bandwidths from the product of the off-chip clock rate and the number of signal pins from the ITRS roadmap. The dashed lines presume that the number of bytes of off-chip interconnect per floating-point operation (i.e., the number of bytes/FLOP) is to be maintained in the later years.

years if we are to meet the full off-chip bandwidths we have calculated from the ITRS roadmap. Without WDM, the width available per channel is less than the fiber diameter. On the other hand, 16-channel WDM together with the ITRS off-chip clock rates in principle would be sufficient for all cases except the 2022 case with constant bytes/FLOP. Thirty-two or 64 channel WDM would give more flexibility in using the perimeter and reduce the number of fibers accordingly. Thirty-two channel WDM with 361 fibers would handle the 780 Tb/s of the 2022 case with constant bytes/FLOP using the ITRS off-chip clock rate of 67.5 GHz. With 100 GHz channel spacing in the WDM, the required spectral width would fit within the telecommunications C-band. Such an approach would allow a direct "chip-to-network" connection.

There would, however, be substantial device challenges for such a system. Specifically, we would need i) optical output devices (modulators or lasers) capable of running at  $\sim\!\!67.5$  GHz rates, with low enough optical energies, and ii) compact optical WDMs with 16, 32, or possibly more channels. If we were to position those multiplexers at the edges of the chip, then we would only have  $\sim\!\!100\!-\!200~\mu\mathrm{m}$  width for each multiplexer depending on how densely we packed the fibers.

Wavelength splitters are already necessary components in telecommunications WDM systems. See [63] and [64] for discussions of recent integrated technology. The conventional approach for wavelength splitters in guided wave systems is to use arrayed waveguide gratings (AWGs) [65]–[67], but even in miniaturized systems [68], these have centimeter sizes too large for the  $\sim$ 100–200  $\mu$ m width available here.

Silicon microring resonators allow compact resonators for filters [69] and have demonstrated four-channel WDM operation [70]. Such rings likely have to be individually tuned in practice, however—e.g., using thermal tuning. The power for such tuning would have to be included in the power budget.

An alternative approach would be to find some more compact approach that could split multiple wavelengths at once, perhaps allowing just one or two global tunings of the structure (e.g., center wavelength and overall channel spacing). Recent work in etched echelle gratings [71], [72] is promising for achieving the necessary sizes for such devices. Another promising concept is to use superprism phenomena in photonic nanostructures. In photonic crystal structures, the beam propagation angle can be strongly dependent on wavelength because of group velocity phenomena (see, e.g., [73]-[78]). With photonic crystal structures, the angle can change nonlinearly with wavelength and the beam form can be distorted, however. A more flexible approach is to use custom-designed nonperiodic structures [79]-[83]. These have shown linear dispersion with wavelength, with smaller size than their crystalline counterparts, and can also show controllable (e.g., steplike [81]) forms of the beam shift with wavelength. Recent

work [84], [85] has attempted to understand the fundamental limits to how small dispersive optical elements could be made, and the results are promising for future very compact devices.

We certainly would need other optical components for such systems. In particular, we need to be able to couple efficiently from external waveguides, such as fibers, to the chips, and there have been various approaches to such coupling (see, e.g., [64] and [86]–[91]).

Whether or not fibers are used to take the information off each chip, to connect even a small fraction of the information from multiple chips to the world outside the board, optical fibers are likely essential. The use of WDM on those external fibers is likely also essential; otherwise the number of fibers would become too large. Hence, we would need to address the issue of compact wavelength splitters for these external connections even if we did not use them for most of the connections to chips.

b) On-board waveguides: Waveguides in silicon technologies can be made in sizes down to less than 1  $\mu$ m. References [92]–[96] summarize developments and recent work in waveguides in silicon technology. Hence, we could contemplate chips attached to a larger silicon substrate or "board" containing optical waveguides. Note that the waveguide spacings in Fig. 5 are larger than 1  $\mu$ m for all cases. Hence, even if we presumed we were taking the waveguide connections off the perimeter of the chip in a single layer of waveguides, we might be able to avoid WDM into and out of those waveguides, and we might be able to modulate at just the on-chip clock rate. The guides would, however, have to be quite small; consequently, loss would become a particularly important parameter.

Of course, any such use of small guides would require very precise alignment between the chip and the silicon optics substrate. An example of a recent approach to such chip to waveguide coupling is given in [89], and various other waveguide coupling approaches [64], [86]–[91] could be applicable here.

2) Free-Space Optical Systems: An alternative to using waveguides to bring the information in and out of the chip is to use "free space" systems that image multiple light beams in and out of the surface of the chips, usually in twodimensional "surface normal" arrays. Such systems have received substantial research attention and laboratory demonstrations [97]-[104]. In this case, imaging optics is used to relay entire arrays of beams from one chip to another. For example, a six-stage system with over 60 000 light beams was demonstrated using such free-space optics [104]. Some earlier work focused on optical interconnected optoelectronic logic device arrays [97]-[99], and later work has investigated CMOS chips with large arrays of optoelectronic devices hybrid attached to the chips [105], [106]. Much of this work used quantum-well diode structures exploiting the strong quantum-confined Stark effect electroabsorption [107] to make the optoelectronic logic or modulator devices. Device arrays with several thousand elements were demonstrated [106]. Other work used vertical cavity surface-emitting laser (VCSEL) arrays (e.g., [100], [101], and [104]).

Free-space optical systems in general have no basic problem in working with quite large arrays of light beams. Ordinary lens systems can readily handle many millions of resolution elements, including focusing to small spots on the scale of micrometers in size. Combinations of conventional lenses and microlens arrays allow efficient focusing to large but sparse arrays of small spots [103], [108]. Techniques based on planar diffractive optical elements, which are fabricated using lithographic patterning, can generate very large regular arrays of spots from a single laser beam and can implement a variety of quite complex regular interconnection patterns [100], [103], [109]. Though random interconnect patterns are difficult for free-space optics, regular structures such as busses or even strongly interleaved patterns such as perfect shuffles that are suited to operations such as Fourier transforms or switching networks could be quite viable. Microoptical systems can make free-space connections from chip to chip or within a chip [110], and a planar optics technology has been demonstrated that could make entire prealigned "free space" optical systems based on lithography on a planar substrate [109].

Free-space optics has the psychological disadvantage that, in bringing information in and out perpendicular to the surface of the chip, it has a physical architecture quite unlike the planar one of chips, boards, and even optical waveguides. An argument sometimes used against such an approach is that we cannot spare a surface of the chip just for optical beams since we already need one chip surface for wiring and another for heat removal. Perhaps that argument could be resolved by the use of transparent heat conductors or mixing functions on a given side of the chip (such as optical and electrical connections). Silicon substrates themselves are, of course, transparent at the infrared wavelengths used in telecommunications.

Because of the large numbers of light beams that can be handled by free-space optics, even for the most extreme case of the 2022 chip with constant byte/FLOP scaling, there would be no need to use any clock rate beyond the onchip rate. At the presumed 14.3 GHz on-chip clock rate of 2022 and considering the most extreme case of interconnects capable of constant bytes/FLOP in the later years, approximately 55 000 surface optical "pads" would be required (see Fig. 4). At an example optical pad size of  $10 \times 10 \ \mu \text{m}^2$ , the total area consumed by the pads would be 5.5 mm<sup>2</sup>, a very small fraction of the 310 mm<sup>2</sup> chip area, so we are not near to any limit of available area. (The pad sizes of such interconnects would be comparable to current 3-D electrical vertical chip-to-chip interconnects [53], but they would not necessarily be restricted to the very close proximity connections of such electrical schemes.)

If we speculate that we could run these surface-normal devices with optical energies  $\sim$ 10 fJ per bit, then the entire

interconnect off the chip could be run with one  $\sim$ 8 W laser even for this extreme case. While that is a high power for one laser, it is not inconceivable. The use of a single laser to drive the interconnect also offers the possibility that all the interconnects could be clocked synchronously and the signals retimed by pulsing the laser itself [32], thus possibly saving clock power in the interconnects. Avoiding running any interconnects at the very high proposed off-chip rates of the electrical interconnects (67.5 GHz for the 2022 chip) could also avoid clocking difficulties and additional power dissipation for the time multiplexers and demultiplexers needed for such systems.

#### **B.** On-Chip Interconnects

The arguments for optics for on-chip interconnects are less compelling than those for off-chip interconnects, at least if considered on the basis of either energy or bandwidth density alone. Here we will briefly discuss the possible system configurations for optics on-chip and some of the resulting criteria. One benefit optics could bring on-chip is to allow long lines at high bandwidth densities, removing such lines as a physical bottleneck.

1) Waveguides: Waveguides in silicon photonics are one interesting and promising approach [92]-[96]. Even small optical guides on the order of a micrometer in size should have low enough loss that such propagation loss itself is not a substantial issue for chip scales [94]. We see from Fig. 5 that, at least if we take a very simplistic view of waveguides, entirely filling one layer on-chip and connecting from the area of the chip to the edges, possibly we could feed the off-chip interconnect using such a layer of guides with signals running at only the on-chip clock rate and without using WDM in the guides. The resulting guides would become very small and close (a 1.3  $\mu$ m pitch) in the extreme case of the 2022 chip with constant bytes/FLOP scaling. To give some flexibility, and/or to allow some guides to be used for internal on-chip connections, higher clock rates, multiple layers of waveguides, or some WDM would likely be required.

Whether such guides could handle the internal on-chip interconnects is an open question, which also depends strongly on the architecture. Above, we considered that the on-chip "global" interconnect requirements might be, e.g., five times the off-chip bandwidth, though such connections might be for shorter distances, e.g., 1/5 of the chip size. In that case, possibly one layer of guides would still be sufficient even without higher interconnect clock rates or WDM, just as in the case of guides to feed the off-chip interconnect.

Nanometallic or plasmonic metal waveguides have been considered for on-chip waveguiding in both single-conductor and two-conductor waveguides [111]–[117]. Such waveguides can be very small, possibly even smaller than dielectric waveguides. Such very small waveguides could concentrate light to very small (e.g., < 100 nm scale)

device volumes [116], which could be useful, for example, for making very small photodetectors. As waveguides for longer interconnects, while they could be a possible approach, the high loss of small guides means in practice that they would have to be comparable to or larger than dielectric guides to achieve comparable and usable overall loss [111]–[116]. A critical analysis of plasmonic waveguides for interconnect has also been given by Tucker [118]. Hence, while they might have uses, they are not a clearly superior solution for the optical "wiring" at substantially higher onchip interconnect densities at the scale of the chip.

2) Free Space: Free-space optics could also connect within a chip, though this has received relatively less attention in the research literature. Many of the schemes used between chips could also be used within chips. We saw in the discussion above of chip-to-chip interconnects that the surface-normal optical pads for off-chip interconnects need take up only a small fraction of the surface area, so there is a large amount of area remaining for pads for on-chip interconnects.

Free-space interconnects suit regular interconnection patterns, so it might be particularly interesting for regular on-chip networks, for example, connecting multiple processors on chip. A free-space approach is certainly an interesting option for delivering clock signals synchronously over an entire chip [29]–[34].

## V. REQUIREMENTS FOR OPTICAL AND OPTOELECTRONIC DEVICES

#### A. Energy Targets

We can draw summary conclusions from the energy targets suggested above as follows.

- i) To be competitive with the current state of the art in electrical off-chip interconnects, the system energy per bit should be  $< 1~\rm pJ$ , and to offer sufficient energy advantage for optics, it should be  $\sim \! 100~\rm fJ/bit$  or lower.

- ii) To meet the demands of off-chip interconnects out to the ITRS projections of 2022, system energies per bit of 100 fJ/bit may sufficient, but to sustain the number of bytes/FLOP in the later years will require 50 fJ/bit or lower system energy.

- iii) To be competitive with near-future electrical global on-chip interconnects, the system energy per bit should be  $\ll 50-200$  fJ/bit.

- iv) To meet global on-chip interconnect demands out to 2022 will require system energies per bit of ~30 fJ/bit on ITRS projections (assuming the global on-chip bandwidth is 5 times the off-chip bandwidth); and to sustain the number of bytes/ FLOP in the later years will require ~10 fJ/bit system energies.

An optical interconnect system needs a transmitter driver circuit, an optical output device (laser or modulator),

an optical channel, a photodetector, and a photodetector circuit. Let us consider the photodetector and receiver first.

1) Photodetector and Receiver Circuit: On the numbers we have been discussing here, provided we can make a reasonably efficient and well-integrated photodetector with a low enough capacitance, the photodetector should not pose a basic challenge in meeting these targets. Per square micrometer of area, a 1- $\mu$ m-thick piece of a typical semiconductor has a capacitance of  $\sim$ 100 aF. Hence photodetectors with areas of a few square micrometers with thickness of  $\sim$ 100 nm or greater will have capacitances of a few femtofarads.

To calculate the total capacitance, we need to estimate the gate capacitance of the transistor with which the detector would be integrated. Calculations based on the publicly available ASU Predictive Technology Model<sup>3</sup> [119], [120] can be used to estimate the gate capacitance of CMOS transistors. For the 90 nm CMOS technology node, the gate capacitance of an NMOS transistor per unit transistor width is estimated to be  $\sim 2$  fF/ $\mu$ m, and for the 32 nm node the corresponding number is  $\sim$ 1.2 fF/ $\mu$ m, at least for transistors that are wide compared to the gate length (the length in the direction from source to drain). Hence, the gate capacitance per unit gate width decreases somewhat, though slower than linearly, with decreasing transistor size. Because the absolute transistor width used in a given circuit is likely to scale approximately with the gate length, the transistor gate capacitance in a given circuit will tend to scale down substantially, and somewhat faster than linearly with the technology node dimension.

For example, presuming a transistor width of ten times the node dimension in each case (as might be typical in transistors used in analog front-ends so as to minimize the effect of fabrication variations), the NMOS transistor gate capacitance would scale from 1.8 fF for the 90 nm node to 380 aF for the 32 nm node. Hence, provided the transistor(s) and the micrometer-scale photodetector are well integrated, the total capacitance of photodetector and input transistor(s) should be on the scale of a few femtofarads. With only a few femtojoules of received optical energy, at ~1 eV photons in an efficient photodetector (i.e., ∼1 electron of current for each incident photon), we would generate a few femtocoulombs of charge, which would swing the photodetector and transistor input by  $\sim$ 1 V, i.e., by a full logic voltage swing. In that case, no voltage amplification would be needed in the front-end receiver circuit—in fact, we could possibly directly drive a CMOS inverter circuit (this is sometimes called a "receiverless" approach [30], meaning there is no receiver voltage amplifier circuit required, and the signals could be fed directly into the logic gates). Since the total energy involved here is a few femtojourles, in a well-designed

integrated system, this photodetector/receiver energy need not be a large fraction of the system energies per bit we have discussed. If the optical received energies are somewhat lower or the capacitance is somewhat higher, it is also possible to put in some voltage amplification without greatly increasing the energies [121]. The consequences of somewhat larger detector capacitance have also been considered by, for example, [21]–[23].

The idea of such an intimate integration at femtofarad capacitance levels is still slightly speculative. There have been recent demonstrations of very tightly integrated detector/transistor combinations using Ge on Si structures [122]-[124]. Ge is generally an interesting detector material because it has large enough absorption in the near infrared to allow photodetectors with micrometer sizes, and it can be process compatible with silicon. Recent work on Ge detectors includes [125]-[132]. Some of these approaches can use the same structure as is also being used as a modulator, possibly simplifying the fabrication overall [130]. An additional concept for low-capacitance and potentially high-speed photodetectors is to use nanometallic structures, such as antennas [133]-[136] or waveguides [111]-[117] to concentrate light into deeply subwavelength active detector volumes. The first such integration with CMOS technology has recently been demonstrated [136].

2) Optical Output Device and Transmitter Circuit: Perhaps the single largest technological challenge in meeting the energy targets we have suggested lies in the device that converts the electrical signal to the optical one. Historically, all such devices have taken substantial energies to operate, much larger than our targets here. If we can make such a device, the energy to drive it from a well-designed transmitter circuit will be comparable to the device operating energy itself, so we can concentrate on discussing the optical output device energy.

The energy targets we need for these devices can only be a moderate fraction of the total system energy per bit; we also need energy for the transmitter circuit, some energy for the receiver, and energy for other circuit functions, possibly including clocking and clock recovery in the link. There will likely also be other energy losses in the system. Given these other energies required in the total system, we set a target here of the optical output device energy/bit being  $\sim 20\%$  of the system energy/bit.

Hence, from the above discussion of systems energy targets, we have optical device energy targets of 10-20~fJ/ bit for off-chip interconnects, and  $\sim 2-10~\text{fJ/bit}$  for on-chip interconnects. With these targets, we can examine some of the possible device technologies.

There are two general categories—modulators and light emitters. Light emitters themselves could be either incoherent [light-emitting diodes (LEDs)] or coherent (lasers), but we can likely immediately eliminate LEDs. Unless an LED is constrained to emit into only one or a very few spatial modes (as is possible at least in principle

<sup>3</sup>http://www.eas.asu.edu/~ptm/.

through Purcell enhancement in a small, high-Q resonator), it is likely too inefficient optically for coupling into a small photodetector. Uncorrelated light of a given wavelength in different spatial modes cannot be combined back into one mode. Though it is not usually stated in this modal form, this principle is known as the constant radiance (or brightness) theorem, and it is protected by the Second Law of Thermodynamics (if we could achieve this recombination with any passive optical component, we could devise an optical system that would allow us to heat up a hot black body with the combined light from two colder black bodies, thus violating the Second Law). Henceforth, we will consider only lasers or modulators.

a) Directly modulated lasers: A state-of-the-art number for energy per bit in a laser is the 286 fJ/bit demonstrated at 35 Gb/s in a 3- $\mu$ m-diameter tapered oxide aperture VCSEL [137]. This number is certainly low enough to be quite interesting for present interconnects, even for chip-to-chip use. For future use to meet the targets here for future years, however, this demonstrated number is not low enough. A key question is whether such an approach could be scaled down to the  $\sim$ 10 fJ range of our targets.

For a light emitter, 10 fJ is a very low energy. At 1 V drive, this 10 fJ corresponds to  $\sim 10^5$  electrically injected electron-hole pairs. Inverting the population (as is certainly required for lasing) in a single quantum-well layer would typically require  $\sim 10^{12}$  carrier pairs/cm<sup>2</sup>, or  $10^4/\mu$ m<sup>2</sup>. Hence, the 10<sup>5</sup> electron-hole pairs from our 10 fJ would be just enough to invert  $\sim 10 \ \mu \text{m}^2$  of one quantum well. Given that there will be other energies involved in running such a laser, to achieve operation at 10 fJ total energy levels, the gain volume would have to be significantly smaller than  $\sim$ 10 nm  $\times$  10  $\mu$ m<sup>2</sup> of one quantum well. Hence, likely more aggressive laser structures would be required. One possibility would be photonic crystal resonator lasers with single quantum dot gain regions [138], for example, though such structures are still the subject of basic research. Such nanoresonator lasers can also have potentially very fast modulation speeds [138] despite the usual difficulty with lasers that higher modulation speeds require quadratically higher current densities. (One recent scheme [139] can mitigate such modulation limits with intracavity modulation, however.)

The above lasers are made from III–V materials. In addition to the Group III and Group V materials being dopants for silicon, there is generally the problem that epitaxial growth of III–V compounds on silicon is lattice mismatched, which leads to crystal defects. Such crystal defects notoriously lead to short device lifetimes in forward-biased devices such as laser diodes. One radical possibility is to grow III–V nanowires on silicon [140]; because the wires can be so small, they can avoid the defect formation process.

III-V lasers have been successfully bonded to silicon [141] with evanescent coupling between the laser and

silicon waveguiding, though these specific lasers themselves likely still have power dissipation too high to be used in direct modulation for the energies per bit of interest here. Such lasers can also be mode-locked [142] to produce short pulses or possibly frequency combs for WDM use, so they are potentially interesting as optical power supplies.

At the time of writing, there is still no electrically pumped laser in a Group IV material, though there have been reports of gain in silicon nanostructures (see, e.g., [143]), and a combination of tensile strain and heavy doping in Ge may allow net gain [144]. For our interconnect applications, any such laser would also have to be very energy efficient and, if it itself is to be modulated to carry the information, capable of high-speed modulation. As we have shown, the energy targets and modulation speeds are difficult even for the III–V lasers that are the highest performance lasers known.

b) Optical modulators and off-chip lasers: Instead of modulating laser sources directly, we can use modulators as the optical output devices. For modulators, we have two broad categories—refractive and absorptive. To use a modulator, we need another source of light to provide the beam of light they modulate. If that light source is off-chip, we have to make the additional effort to couple that power onto the chip. Putting the source off-chip also has advantages, however. We remove the additional power dissipation of the source itself from the chip. We can centrally control laser wavelength, spectral purity, polarization, and beam form, removing any precise stabilization and control from the relatively harsh environment of the silicon chip. We can use that central laser to clock the entire system [30], [32]. Multiple wavelength "comb" sources are also possible, e.g., by mode-locking [145], giving a set of equally spaced wavelengths suitable for WDM systems. Such a system is also likely easier to fabricate and control if it is off of the chip.

It may be possible to run the entire off-chip interconnect or even possibly the global on-chip interconnect using a single laser, as we mentioned briefly above. Of course, we would also have to deal with coupling losses in such a system.

Refractive modulators: Refractive devices modulate by interfering a beam with itself in some way, either in a single-pass two-beam interference as in a Mach–Zehnder interferometer structure or in some device with multiple interference, such as a resonator. Changing the relative phase of the interfering beams by changing the refractive index changes the output power.

A basic difficulty with refractive modulators is that we have no high-speed mechanism that can usefully give us refractive index changes much larger than  $\sim\!\!10^{-3}$ . Larger index changes can be induced, e.g., in semiconductors very near to their optical absorption edge (see, e.g., [146]), but then such large changes only occur in the presence of substantial absorption. Even with  $\Delta n \sim 10^{-3}$ , to get a half-wavelength path-length change at 1.5  $\mu m$  wavelength

would require a device length  $L\sim750~\mu\mathrm{m}$  if we changed the index in only one arm. Hence generally Mach–Zehnder modulators have lengths in the hundreds of micrometers or longer.

There has been considerable interest in such two-beam interferometer approaches in silicon photonics (see, e.g., [147]). Because the main refractive index change mechanism available in silicon (free-carrier index change [148]) is relatively weak, such devices necessarily take substantial energy on the scale of interest here. For example, Green *et al.* [149] show 5 pJ/bit at 10 Gb/s in well-optimized  $100-200-\mu$ m-long devices, much larger than our target numbers.

To make compact refractive modulators, we need to use resonators or possibly slow light [150] to enhance the effect of changing the refractive index in only a smaller length of material. The silicon microring resonator has received much attention (see, e.g., [151]-[156]). Such devices might be able to achieve operating energies in the range of tens of femtojourles and could be very small, e.g., a few micrometers in diameter [152]. The resonators need quite large quality factor (Q) (e.g., > 10 000 [153]), however, meaning that they have very narrow resonances (e.g., 0.04 nm wavelength range [153]) that have to be precisely tuned. Often that tuning is by temperature, and that temperature would have to be stabilized precisely also to hold the device on resonance (e.g., to a small fraction of a degree Kelvin based on the  $\sim 2 \times 10^{-4}/K$  temperature dependence of silicon's refractive index [153]). The width of the resonance is also so narrow that it is one of the limits on modulation speed, though modulation above 10 Gb/s is quite possible [151]. An important point in the energy per bit is that the thermal tuning power must be included in estimating the total system power requirement. The required tuning power is not yet clear, but a hypothetical tuning power of 1 mW for a 10 Gb/s modulator would correspond to an additional effective 100 fJ/bit, which would take the energy out of our target range. Such devices do, however, have the advantage that they are automatically also wavelength filters and can perform WDM switching functions as well (see, e.g., [69] and [70]).

Electroabsorption modulators work by changing the optical absorption in a semiconductor structure by applying voltage to it. There are two related mechanisms, the Franz–Keldysh effect, seen in bulk semiconductors and the quantum-confined Stark effect (QCSE) [107], seen in quantum-confined structures such as thin (e.g.,  $\sim 10$  nm) quantum-well layers. These effects are very closely related [155], with the Franz–Keldysh effect being the limit of the QCSE as the quantum-well layers are made thicker. The QCSE has more spectrally abrupt and somewhat stronger changes in absorption coefficient as a consequence of the discretization of the density of states and the stronger excitonic effects in quantum-confined structures.

Both effects require operating electric fields in the range of 1–10 V/ $\mu$ m (10<sup>4</sup>–10<sup>5</sup> V/cm). Such fields are

readily obtained by reverse biasing p - i - n diodes that contain the bulk semiconductor or quantum well materials in the intrinsic (i) region of the diodes. Both effects are seen near the direct bandgap optical absorption edge and give rise to increases in the optical absorption below the bandgap photon. The Franz-Keldysh effect gives a long, smooth absorption "tail," with typical induced absorption coefficient values in the range of a few hundred cm<sup>-1</sup>. The QCSE gives more abrupt steps in absorption that shift to lower energy with field, with absorption coefficient values that can be up to several thousand cm<sup>-1</sup>. With their weaker absorption coefficients, Franz-Keldysh devices are used in waveguide structures that can have the necessary longer interaction lengths. QCSE devices are used in waveguide structures too, but, with their stronger absorption coefficient changes, they can be used for "surface normal" devices of micrometer vertical dimensions (see, e.g., [106]. QCSE modulators are widely used in telecommunications, especially in integrated laser-modulator structures (see, e.g., [156]).

Such electroabsorption modulators do not rely on changing the carrier density in the structure, and so they avoid some of the speed limitations found in directly modulated lasers or in silicon carrier density index shift modulators. They are thought theoretically to have fundamental speed limits well below a picosecond [157]. Quantum-well modulator devices have been tested at high speeds [158], [159] and up to 500 Gb/s effective modulation rate [160].

These electroabsorption mechanisms are very strong; the QCSE may be the strongest high-speed electroabsorption effect, enabling modulators with only a few micrometers of optical path length even without the use of resonators. The performance can also be enhanced by cavities if desired (see, e.g., [161]–[163] for recent examples). Because of the strength of the effects, only modest cavity Q or finesse has been used so far. Devices have also been demonstrated with <1 V drive swing (e.g., [161] and [163]), as practically required for compatibility with CMOS technology.